EN: This Datasheet is presented by the manufacturer.

Please visit our website for pricing and availability at www.hestore.hu.

# 1T 8051 8-bit Microcontroller

# NuMicro® Family MS51 Series MS51BA9AE MS51DA9AE Datasheet

nuvoTon

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

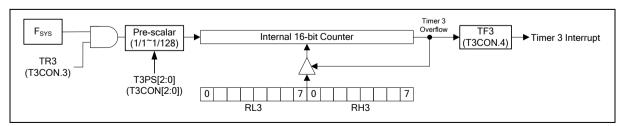

# TABLE OF CONTENTS GENERAL DESCRIPTION ......6 3 PARTS INFORMATION ......10 3.1 MS51 Series Package Type......10 4.1.1 TSSOP 14-pin Package Pin Diagram ......12 4.1.2 MSOP 10-pin Package Pin Diagram ......12 6 FUNCTION DESCRIPTION ......16 6.4.1 In-Application-Programming (IAP) ......23 6.4.2 In-Circuit-Programming (ICP) ......23 6.4.3 On-Chip-Debugger (OCD) ......23 6.5 General Purpose I/O (GPIO) ......24 6.6.1 Timer/Counter 0 And 1......25 6.6.2 Timer2 and Input Capture ......25 6.7 Watchdog Timer (WDT)......27 6.10 6.11 6.12 12-Bit Analog-To-Digital Converter (ADC) .......33 6.13

nuvoton

| 7  | APPLICATION CIRCUIT                                                   | 34 |

|----|-----------------------------------------------------------------------|----|

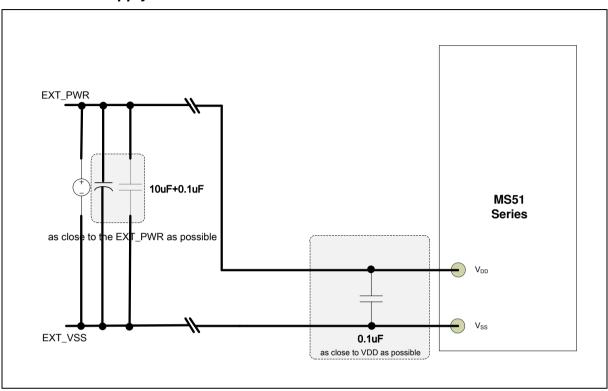

|    | 7.1 Power Supply Scheme                                               | 34 |

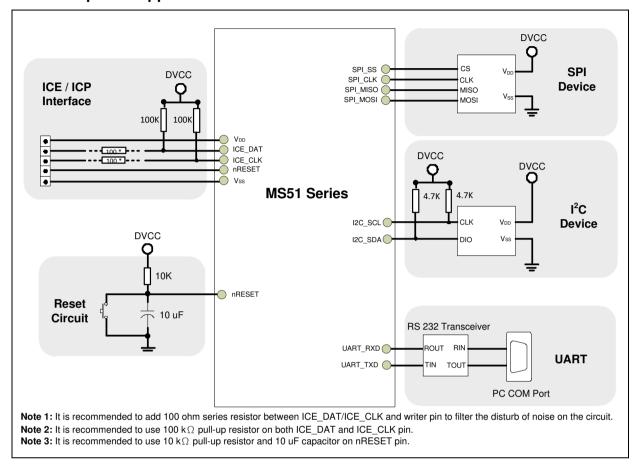

|    | 7.2 Peripheral Application Scheme                                     | 35 |

| 8  | ELECTRICAL CHARACTERISTICS                                            | 36 |

|    | 8.1 General Operating Conditions                                      | 36 |

|    | 8.2 DC Electrical Characteristics                                     | 37 |

|    | 8.2.1 Supply Current Characteristics                                  | 39 |

|    | 8.2.3 I/O DC Characteristics                                          |    |

|    | 8.3.1 Internal High Speed 16MHz RC Oscillator (HIRC)                  |    |

|    | 8.3.2 External 4~24 MHz High Speed Clock Input Signal Characteristics | 45 |

|    | 8.3.4 I/O AC Characteristics                                          | 47 |

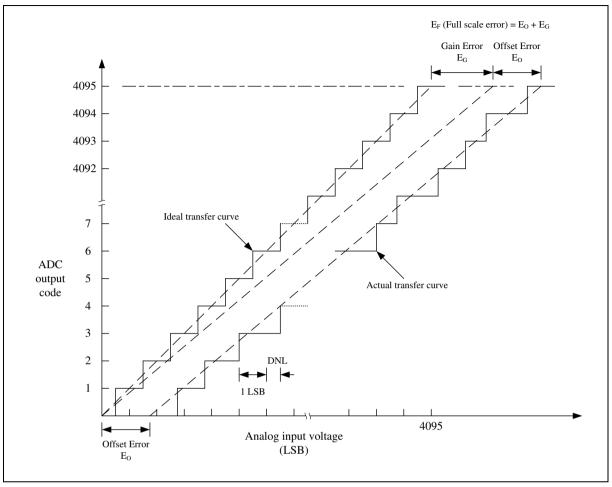

|    | 8.4 Analog Characteristics                                            | 48 |

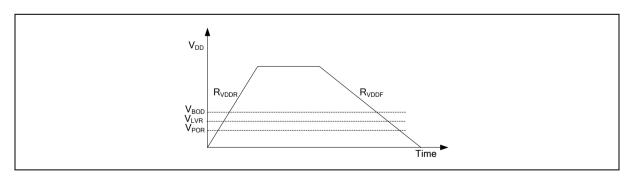

|    | 8.4.1 Reset and Power Control Block Characteristics                   |    |

|    | 8.5 Flash DC Electrical Characteristics                               |    |

|    | 8.6 Absolute Maximum Ratings                                          | 53 |

|    | 8.6.1 Voltage Characteristics                                         | 53 |

|    | 8.6.3 Thermal Characteristics                                         | 54 |

|    | 8.6.5 Package Moisture Sensitivity(MSL)                               |    |

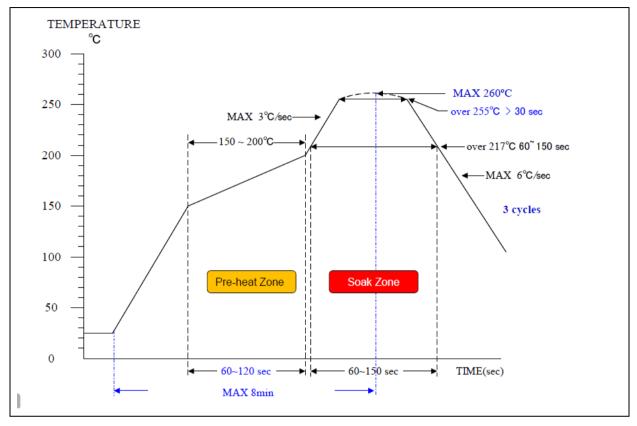

|    | 8.6.6 Soldering Profile                                               |    |

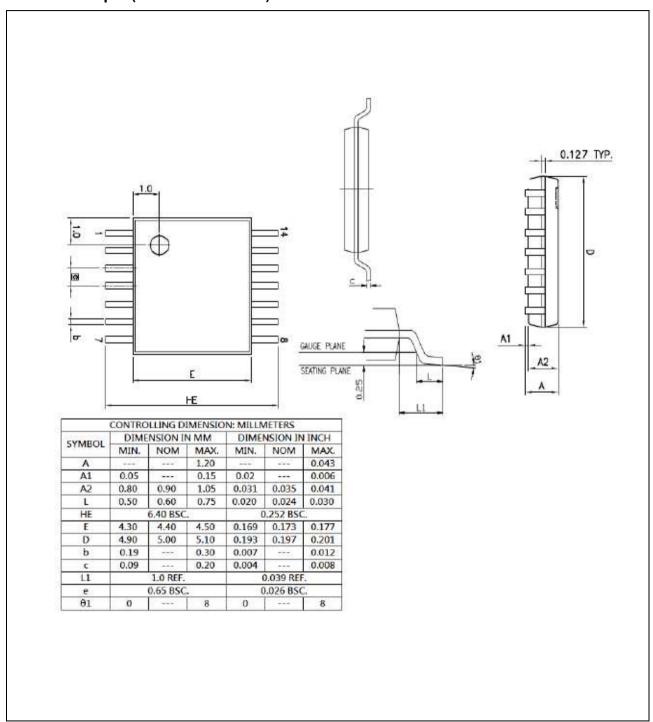

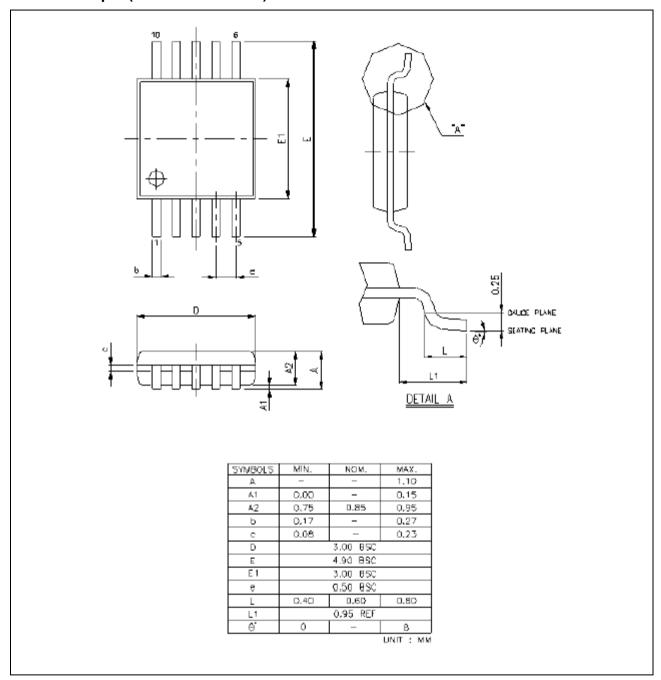

| 9  | PACKAGE DIMENSIONS                                                    | 58 |

|    | 9.1 TSSOP 14-pin (4.4 x 5.5 x 1.2 mm)                                 | 58 |

|    | 9.2 MSOP 10-pin (3.0 x 3.0 x 1.1 mm)                                  | 59 |

| 10 | ) ABBREVIATIONS                                                       | 60 |

|    | 10.1 Abbreviations                                                    | 60 |

| 11 | REVISION HISTORY                                                      | 61 |

# **LIST OF FIGURES**

nuvoTon

| Figure 4.1-1 Pin Assignment of TSSOP-14 Package         | 12 |

|---------------------------------------------------------|----|

| Figure 4.1-2 Pin Assignment of MSOP-10 Package          | 12 |

| Figure 5.1-1 Functional Block Diagram                   | 15 |

| Figure 6.2-1 CONFIG0 Any Reset Reloading                | 18 |

| Figure 6.2-2 CONFIG2 Power-On Reset Reloading           | 20 |

| Figure 6.3-1 Clock System Block Diagram                 | 22 |

| Figure 6.6-1 Timer 2 Full Function Block Diagram        | 26 |

| Figure 6.6-2 Timer 3 Block Diagram                      | 26 |

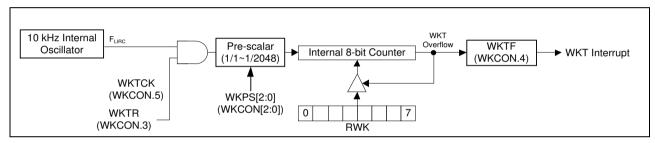

| Figure 6.8-1 Self Wake-Up Timer Block Diagram           | 28 |

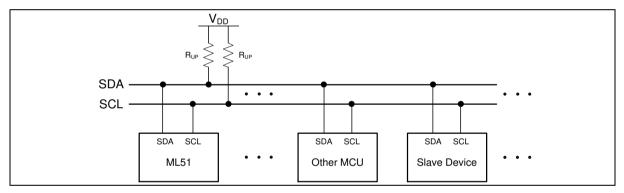

| Figure 6.11-1 I <sup>2</sup> C Bus Interconnection      | 31 |

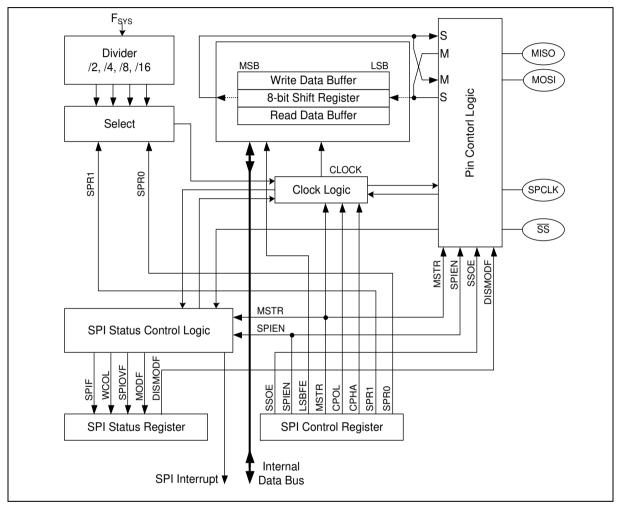

| Figure 6.12-1 SPI Block Diagram                         | 32 |

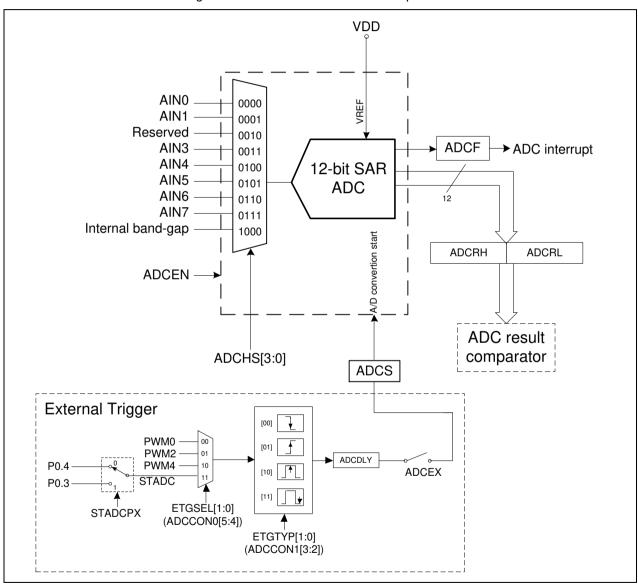

| Figure 6.13-112-bit ADC Block Diagram                   | 33 |

| Figure 7.1-1 Numara® MS51 Power Supply Circuit          | 34 |

| Figure 7.2-1 NuMicro® MS51 Peripheral Interface Circuit | 35 |

| Figure 8.6-1 Soldering profile from J-STD-020C          | 57 |

| Figure 9.1-1 TSSOP-14 Package Dimension                 | 58 |

| Figure 9.2-1 MSOP -10 Package Dimension                 | 59 |

| List of Tables                                                             |    |

|----------------------------------------------------------------------------|----|

| Table 3.2-1 MS51 Series Selection Table                                    | 10 |

| Table 3.3-1 MS51 Series Selection Code                                     | 11 |

| Table 4.2-1 Pin Description                                                | 14 |

| Table 6.5-1 Configuration for Different I/O Modes                          | 24 |

| Table 6.7-1 Watchdog Timer-out Interval Under Different Pre-scalars        | 27 |

| Table 8.1-1 General operating conditions                                   | 36 |

| Table 8.2-1 Current Consumption In Normal Run Mode                         | 37 |

| Table 8.2-2 Current Consumption In Idle Mode                               | 38 |

| Table 8.2-3 Chip Current Consumption In Power Down Mode                    | 38 |

| Table 8.2-4 Low-Power Mode Wakeup Timings                                  | 39 |

| Table 8.2-5 I/O Input Characteristics                                      | 40 |

| Table 8.2-6 I/O Output Characteristics                                     | 41 |

| Table 8.2-7 nRESET Input Characteristics                                   | 42 |

| Table 8.3-1 16 MHz Internal High Speed RC Oscillator(HIRC) Characteristics | 43 |

| Table 8.3-2 24 MHz Internal High Speed RC Oscillator(HIRC) characteristics | 44 |

| Table 8.3-3 External 4~24 MHz High Speed Clock Input Signal                | 45 |

| Table 8.3-4 10 kHz Internal Low Speed RC Oscillator(LIRC) Characteristics  | 46 |

| Table 8.3-5 I/O AC Characteristics                                         | 47 |

| Table 8.4-1 Reset And Power Control Unit                                   | 48 |

| Table 8.4-2 Minimum Brown-Out Detect Pulse Width                           | 49 |

| Table 8.5-1 Flash Memory Characteristics                                   | 52 |

| Table 8.6-1 Voltage Characteristics                                        | 53 |

| Table 8.6-2 Current Characteristics                                        | 53 |

| Table 8.6-3 Thermal Characteristics                                        | 54 |

| Table 8.6-4 EMC Characteristics                                            | 55 |

| Table 8.6-5 Package Moisture Sensitivity(MSL)                              | 56 |

| Table 8.6-6 Soldering Profile                                              | 57 |

| Table 10.1-1 List of Abbreviations                                         | 60 |

## GENERAL DESCRIPTION

nuvoton

The MS51 is an embedded flash type, 8-bit high performance 1T 8051-based microcontroller. The instruction set is fully compatible with the standard 80C51 and performance enhanced.

The MS51BA9AE / MS51DA9AE Bytes of main Flash called APROM, in which the contents of User Code resides. The MS51 Flash supports In-Application-Programming (IAP) function, which enables onchip firmware updates. IAP also makes it possible to configure any block of User Code array to be used as non-volatile data storage, which is written by IAP and read by IAP or MOVC instruction, this function means whole 8K Bytes area all can be use as Data Flash through IAP command. MS51 support an function of configurationable Flash from APROM called LDROM, in which the Boot Code normally resides for carrying out In-System-Programming (ISP). The LDROM size is configurable with a maximum of 4K Bytes by CONFIG define. There is an additional include special 128 bytes security protection memory (SPROM) to enhance the security and protection of customer application. To facilitate programming and verification, the Flash allows to be programmed and read electronically by parallel Writer or In-Circuit-Programming (ICP). Once the code is confirmed, user can lock the code for security.

The MS51BA9AE / MS51DA9AE provides rich peripherals including 256 Bytes of SRAM, 1K Bytes of auxiliary RAM (XRAM), Up to 12 general purpose I/O, two 16-bit Timers/Counters 0/1, one 16-bit Timer2 with three-channel input capture module, one Watchdog Timer (WDT), one Self Wake-up Timer (WKT), one 16-bit auto-reload Timer3 for general purpose or baud rate generator, two UARTs with frame error detection and automatic address recognition, one SPI, one I<sup>2</sup>C, five enhanced PWM output channels, eight-channel shared pin interrupt for all I/O, and one 12-bit ADC. The peripherals are equipped with 18 sources with 4-level-priority interrupts capability.

The MS51BA9AE / MS51DA9AE is equipped with three clock sources and supports switching on-thefly via software. The three clock sources include external clock input, 10 kHz internal oscillator, and one 16 MHz internal precise oscillator that is factory trimmed to ±1% at room temperature. The MS51 provides additional power monitoring detection such as power-on reset and 4-level brown-out detection, which stabilizes the power-on/off sequence for a high reliability system design.

The MS51BA9AE / MS51DA9AE microcontroller operation consumes a very low power with two economic power modes to reduce power consumption — Idle and Power-down mode, which are software selectable. Idle mode turns off the CPU clock but allows continuing peripheral operation. Power-down mode stops the whole system clock for minimum power consumption. The system clock of the MS51 can also be slowed down by software clock divider, which allows for a flexibility between execution performance and power consumption.

With high performance CPU core and rich well-designed peripherals, the MS51 benefits to meet a general purpose, home appliances, or motor control system accomplishment.

# 2 FEATURES

| Core and System             |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8051                        | <ul> <li>Fully static design 8-bit high performance 1T 8051-based CMOS microcontroller.</li> <li>Instruction set fully compatible with MCS-51.</li> <li>4-priority-level interrupts capability.</li> <li>Dual Data Pointers (DPTRs).</li> </ul>                                                                                                                                                                                 |

| Power On Reset (POR)        | POR with 1.15V threshold voltage level                                                                                                                                                                                                                                                                                                                                                                                          |

| Brown-out Detector<br>(BOD) | <ul> <li>4-level selection, with brown-out interrupt and reset option.<br/>(4.4V / 3.7V / 2.7V / 2.2V)</li> </ul>                                                                                                                                                                                                                                                                                                               |

| Low Voltage Reset (LVR)     | LVR with 2.0V threshold voltage level                                                                                                                                                                                                                                                                                                                                                                                           |

| Security                    | <ul> <li>96-bit Unique ID (UID)</li> <li>128-bit Unique Customer ID (UCID)</li> <li>128-bytes security protection memory SPROM</li> </ul>                                                                                                                                                                                                                                                                                       |

| Memories                    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Flash                       | <ul> <li>8 KBytes of APROM for User Code.</li> <li>4/3/2/1 Kbytes of Flash for loader (LDROM) configure from APROM for In-System-Programmable (ISP)</li> <li>Flash Memory accumulated with pages of 128 Bytes from APROM by In-Application-Programmable (IAP) means whole APROM can be use as Data Flash</li> <li>An additional 128 bytes security protection memory SPROM</li> <li>Code lock for security by CONFIG</li> </ul> |

| SRAM                        | <ul> <li>256 Bytes on-chip RAM.</li> <li>Additional 1 KBytes on-chip auxiliary RAM (XRAM) accessed<br/>by MOVX instruction.</li> </ul>                                                                                                                                                                                                                                                                                          |

| Clocks                      |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Internal Clock Source       | <ul> <li>Default 16 MHz high-speed internal oscillator (HIRC) trimmed to ±1% (accuracy at 25 °C, 3.3 V).</li> <li>Selectable 24 MHz high-speed internal oscillator (HIRC).</li> <li>10 kHz low-speed internal oscillator (LIRC) calibrating to ±1% by software from high-speed internal oscillator</li> </ul>                                                                                                                   |

| Timers                      |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16-bit Timer                | Two 16-bit Timers/Counters 0 and 1 compatible with                                                                                                                                                                                                                                                                                                                                                                              |

| Feb 08 2022                 | Page <b>7</b> of 62 Rev 1 04                                                                                                                                                                                                                                                                                                                                                                                                    |

nuvoTon

|                        | standard 8051.                                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

|                        | <ul> <li>One 16-bit Timer2 with three-channel input capture module<br/>and 9 input pin can be selected.</li> </ul> |

|                        | <ul> <li>One 16-bit auto-reload Timer3, which can be the baud rate<br/>clock source of UART0 and UART1.</li> </ul> |

|                        | 6-bit free running up counter for WDT time-out interval.                                                           |

| Watchdog               | <ul> <li>Selectable time-out interval is 6.40 ms ~ 1.638s since<br/>WDT_CLK = 10 kHz (LIRC).</li> </ul>            |

| -                      | <ul> <li>Able to wake up from Power-down or Idle mode</li> </ul>                                                   |

|                        | Interrupt or reset selectable on watchdog time-out                                                                 |

|                        | 16-bit free running up counter for time-out interval.                                                              |

|                        | Clock sources from LIRC                                                                                            |

| Wake-up Timer          | <ul> <li>Able self Wake-up wake up from Power-down or Idle mode,<br/>and auto reload count value.</li> </ul>       |

|                        | Supports Interrupt                                                                                                 |

|                        | Up To 5 channel output pins can be selected                                                                        |

|                        | <ul> <li>Supports maximum clock source frequency up to 24 MHz</li> </ul>                                           |

|                        | <ul> <li>Supports independent mode for PWM output</li> </ul>                                                       |

|                        | <ul> <li>Supports complementary mode for up to 2 complementary paired PWM output channels</li> </ul>               |

| PWM                    | <ul> <li>Dead-time insertion with 8-bit resolution</li> </ul>                                                      |

|                        | <ul> <li>Supports 16-bit resolution PWM counter</li> </ul>                                                         |

|                        | Supports mask function and tri-state enable for each PWM pin                                                       |

|                        | Supports brake function                                                                                            |

|                        | <ul> <li>Supports trigger ADC on the following events</li> </ul>                                                   |

| Analog Interfaces      |                                                                                                                    |

|                        | <ul> <li>Analog input voltage range: 0 ~ AV<sub>DD</sub>.</li> </ul>                                               |

|                        | <ul> <li>12-bit resolution and 10-bit accuracy is guaranteed.</li> </ul>                                           |

|                        | <ul> <li>Up to 7 single-end analog input channels</li> </ul>                                                       |

| Analog-to-Digital      | <ul> <li>1 internal channels, they are band-gap voltage (VBG).</li> </ul>                                          |

| Converter (ADC)        | <ul> <li>Up to 500 ksps sampling rate.</li> </ul>                                                                  |

|                        | Software Write 1 to ADCS bit.                                                                                      |

|                        | External pin (STADC) trigger                                                                                       |

|                        | PWM trigger.                                                                                                       |

| Communication Interfac |                                                                                                                    |

|                        |                                                                                                                    |

| UART                   | Supports up to 2 UARTs: UART0 & UART1                                                                              |

|                        |                                                                                                                    |

|                  | <ul> <li>Full-duplex asynchronous communications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <ul> <li>Programmable 9<sup>th</sup> bit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | <ul> <li>UART0_TXD and UART0_RXD pins exchangeable via software.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                  | 1 set of I <sup>2</sup> C devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Master/Slave mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | <ul> <li>Bidirectional data transfer between masters and slaves</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 120              | <ul> <li>Multi-master bus (no central master)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| l <sup>2</sup> C | <ul> <li>7-bit addressing mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FC               | <ul> <li>Standard mode (100 kbps) and Fast mode (400 kbps).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | <ul> <li>Supports 8-bit time-out counter requesting the I<sup>2</sup>C interrupt if<br/>the I<sup>2</sup>C bus hangs up and timer-out counter overflows</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | <ul> <li>Supports hold time programmable</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  | 1 set of SPI devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI              | Supports Master or Slave mode operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SFI              | <ul> <li>Supports MSB first or LSB first transfer sequence</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | <ul> <li>slave mode up to 12 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO             | <ul> <li>Four I/O modes:         <ul> <li>Quasi-bidirectional mode</li> <li>Push-Pull Output mode</li> <li>Open-Drain Output mode</li> <li>Input only with high impendence mode</li> </ul> </li> <li>Schmitt trigger input / TTL mode selectable.</li> <li>Each I/O pin configured as interrupt source with edge/level trigger setting</li> <li>Standard interrupt pins INTO and INTT.</li> <li>Supports high drive and high sink current I/O</li> <li>I/O pin internal pull-up or pull-down resistor enabled in input mode.</li> <li>Maximum I/O Speed is 24 MHz</li> <li>Each GPIO enabling the pin interrupt function will also enable the wake-up function</li> </ul> |

| ESD & EFT        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ESD              | HBM pass 8 kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EFT              | • > ± 4.4 kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Latch-up         | • 150 mA pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### 3 **PARTS INFORMATION**

nuvoTon

#### **MS51 Series Package Type** 3.1

|             | MSOP10    | TSSOP14   | TSSOP20                | QFN20                               | TSSOP28                | LQFP32    | QFN33     |

|-------------|-----------|-----------|------------------------|-------------------------------------|------------------------|-----------|-----------|

| Part<br>No. | MS51BA9AE | MS51DA9AE | MS51FB9AE<br>MS51FC0AE | MS51XB9AE<br>MS51XB9BE<br>MS51XC0BE | MS51EC0AE<br>MS51EB0AE | MS51PC0AE | MS51TC0AE |

#### 3.2 **MS51 Series Selection Guide**

|             |            |           |              |     |        |    |                            | Conne | ctivity |     |             |                      |

|-------------|------------|-----------|--------------|-----|--------|----|----------------------------|-------|---------|-----|-------------|----------------------|

| Part Number | Flash (KB) | SRAM (KB) | ISP ROM (KB) | 0/1 | Timer/ | MW | ISO 7816 -3 <sup>[2]</sup> | UART  | IdS     | l²C | ADC(12-Bit) | Package              |

| MS51BA9AE   | 8          | 1         | 4            | 8   | 4      | 5  | -                          | 2     | -       | 1   | 5-ch        | MSOP10               |

| MS51DA9AE   | 8          | 1         | 4            | 12  | 4      | 5  | -                          | 2     | 1       | 1   | 7-ch        | TSSOP14              |

| MS51XB9AE   | 16         | 1         | 4            | 18  | 4      | 6  | -                          | 2     | 1       | 1   | 8-ch        | QFN20 <sup>[3]</sup> |

| MS51XB9BE   | 16         | 1         | 4            | 18  | 4      | 6  | -                          | 2     | 1       | 1   | 8-ch        | QFN20 <sup>[3]</sup> |

| MS51FB9AE   | 16         | 1         | 4            | 18  | 4      | 6  | -                          | 2     | 1       | 1   | 8-ch        | TSSOP20              |

| MS51EB0AE   | 16         | 2         | 4            | 26  | 4      | 11 | 3                          | 2     | 1       | 1   | 15-ch       | TSSOP28              |

| MS51FC0AE   | 32         | 2         | 4            | 18  | 4      | 8  | 2                          | 2     | 1       | 1   | 10-ch       | TSSOP20              |

| MS51XC0BE   | 32         | 2         | 4            | 18  | 4      | 8  | 2                          | 2     | 1       | 1   | 10-ch       | QFN20                |

| MS51EC0AE   | 32         | 2         | 4            | 26  | 4      | 10 | 3                          | 2     | 1       | 1   | 15-ch       | TSSOP28              |

| MS51PC0AE   | 32         | 2         | 4            | 30  | 4      | 12 | 3                          | 2     | 2       | 1   | 15-ch       | LQFP32               |

| MS51TC0AE   | 32         | 2         | 4            | 30  | 4      | 12 | 3                          | 2     | 2       | 1   | 15-ch       | QFN33                |

### Note:

- 1. ISP ROM programmable 1K/2K/3K/4KB Flash for user program loader (LDROM) share from ARPOM.

- 2. ISO 7816-3 configurable as UART2.

- Detailed package information please refer to Chapter 7

- This TRM only for MS51BA9AE / MS51DA9AE product

Table 3.2-1 MS51 Series Selection Table

# 3.3 MS51 Series Selection Code

| MS       | 51       | F                       | В        | 9          | Α       | Е              |

|----------|----------|-------------------------|----------|------------|---------|----------------|

| Core     | Line     | Package                 | Flash    | SRAM       | Reserve | Temperature    |

| 1T 8051  | 51: Base | B: MSOP10 (3x3 mm)      | A: 8 KB  | 0: 2 KB    |         | E:-40 ~ 105° C |

| Industry |          | D: TSSOP14 (4.4x5.0 mm) | B: 16 KB | 1: 4 KB    |         |                |

|          |          | E: TSSOP28 (4.4x9.7 mm) | C: 32 KB | 2: 8/12 KB |         |                |

|          |          | F: TSSOP20 (4.4x6.5 mm) |          | 3: 16 KB   |         |                |

|          |          | I: SOP8 (4x5mm)         |          | 6: 32 KB   |         |                |

|          |          | O: SOP20 (300 mil)      |          | 8: 64 KB   |         |                |

|          |          | P: LQFP32 (7x7 mm)      |          | 9: 1 KB    |         |                |

|          |          | T: QFN33 (4x4 mm)       |          | A: 96 KB   |         |                |

|          |          | U: SOP28 (300 mil)      |          |            |         |                |

|          |          | X: QFN20 (3x3mm)        |          |            |         |                |

Table 3.3-1 MS51 Series Selection Code

## PIN CONFIGURATION

nuvoTon

Users can find pin configuration informations by using NuTool - PinConfigure. The NuTool -PinConfigure contains all Nuvoton NuMicro® Family chip series with all part number, and helps users configure GPIO multi-function correctly and handily.

#### 4.1 MS51BA9AE / MS51DA9AE Multi Function Pin Diagram

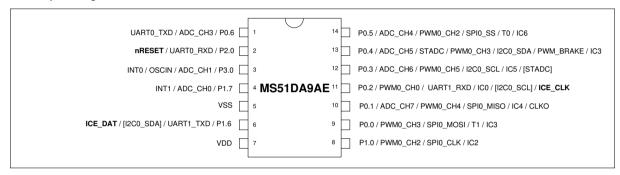

#### 4.1.1 TSSOP 14-pin Package Pin Diagram

Corresponding Part Number: MS51DA9AE

Figure 4.1-1 Pin Assignment of TSSOP-14 Package

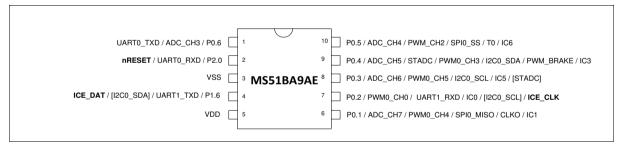

#### 4.1.2 MSOP 10-pin Package Pin Diagram

Corresponding Part Number: MS51BA9AE

Figure 4.1-2 Pin Assignment of MSOP-10 Package

# 4.2 MS51BA9AE / MS51DA9AE Pin Description

| Pin Number |           |                          |                                                                                       |

|------------|-----------|--------------------------|---------------------------------------------------------------------------------------|

| MS51DA9AE  | MS51BA9AE | Symbol                   | Multi-Function Description <sup>[1]</sup>                                             |

| 7          | 5         | VDD                      | Supply voltage VDD for operation.                                                     |

| 5          | 3         | VSS                      | Ground potential.                                                                     |

|            |           | P0.0                     | Port 0 bit 0.                                                                         |

|            |           | PWM0_CH3                 | PWM output channel 3.                                                                 |

| 9          | -         | SPI0_MOSI                | SPI master output/slave input.                                                        |

|            |           | IC3                      | Input capture channel 3.                                                              |

|            |           | T1                       | External count input to Timer/Counter 1 or its toggle output.                         |

|            |           | P0.1                     | Port 0 bit 1.                                                                         |

|            |           | ADC_CH7                  | ADC input channel 7                                                                   |

| 10         | 6         | PWM0_CH4                 | PWM output channel 4.                                                                 |

| 10         | 6         | SPI0_MISO                | SPI master input/slave output.                                                        |

|            |           | IC4                      | Input capture channel 4.                                                              |

|            |           | CLKO                     | Clock output                                                                          |

|            |           | P0.2                     | Port 0 bit 2.                                                                         |

|            |           | ICE_CLK                  | ICP clock input.                                                                      |

|            |           |                          | <b>Note:</b> It is recommended to use 100 k $\Omega$ pull-up resistor on ICE_CLK pin. |

| 11         | 7         | PWM0_CH0                 | PWM0 channel 0                                                                        |

|            |           | UART1_RXD <sup>[2]</sup> | Serial port 1 receive input.                                                          |

|            |           | IC0                      | Input Capture channel 0                                                               |

|            |           | [I2C0_SCL]               | I <sup>2</sup> C clock.                                                               |

|            | 8         | P0.3                     | Port 0 bit 3.                                                                         |

|            |           | ADC_CH6                  | ADC input channel 6                                                                   |

| 12         |           | PWM0_CH5                 | PWM output channel                                                                    |

| 12         |           | I2C0_SCL                 | I <sup>2</sup> C0 clock pin                                                           |

|            |           | IC5                      | Input capture channel 5.                                                              |

|            |           | [STADC]                  | External start ADC trigger                                                            |

|            |           | P0.4                     | Port 0 bit 4.                                                                         |

|            |           | ADC_CH5                  | ADC input channel 5.                                                                  |

|            |           | PWM0_CH3                 | PWM output channel 3.                                                                 |

| 13         | 9         | PWM0_BRAKE               | PWM0 Fault Brake input.                                                               |

|            |           | I2C0_SDA                 | I <sup>2</sup> C0 data pin                                                            |

|            |           | IC3                      | Input capture channel 3.                                                              |

|            |           | STADC                    | External start ADC trigger                                                            |

|            |           | P0.5                     | Port 0 bit 5.                                                                         |

|            |           | ADC_CH4                  | ADC input channel 4                                                                   |

| 14         | 10        | PWM0_CH2                 | PWM output channel 2.                                                                 |

|            | 10        | SPI0_SS                  | SPI0 slave select input.                                                              |

|            |           | IC6                      | Input capture channel 6.                                                              |

|            |           | Т0                       | External count input to Timer/Counter 0 or its toggle output.                         |

|            |           | P0.6                     | Port 0 bit 6.                                                                         |

| 1          | 1         | ADC_CH3                  | ADC input channel 3.                                                                  |

|            |           | UART0_TXD                | Serial port 0 transmit data output.                                                   |

|            |           | P1.0                     | Port 1 bit 0.                                                                         |

| 8          |           | PWM0_CH2                 | PWM output channel 2.                                                                 |

| 0          | -         | SPI0_CLK                 | SPI clock.                                                                            |

|            |           | IC2                      | Input capture channel 2.                                                              |

|            |           | P1.6                     | Port 1 bit 6.                                                                         |

| 6          | 4         | ICE_DAT                  | ICP / ICE data input or output.                                                       |

|            |           | ICE_DAT                  | <b>Note:</b> It is recommended to use 100 k $\Omega$ pull-up resistor on ICE_DAT pin. |

| Pin Nu    | umber     | Orangh al                | Motification Description[1]                                                                                                                                                                                                                                                                                                                |

|-----------|-----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MS51DA9AE | MS51BA9AE | Symbol                   | Multi-Function Description <sup>[1]</sup>                                                                                                                                                                                                                                                                                                  |

|           |           | UART1_TXD <sup>[2]</sup> | Serial port 1 transmit data output.                                                                                                                                                                                                                                                                                                        |

|           |           | [I2C0_SDA]               | I2C data.                                                                                                                                                                                                                                                                                                                                  |

|           |           | P1.7                     | Port 1 bit 7.                                                                                                                                                                                                                                                                                                                              |

| 4         | -         | ADC_CH0                  | ADC input channel 0.                                                                                                                                                                                                                                                                                                                       |

|           |           | INT1                     | External interrupt 1 input.                                                                                                                                                                                                                                                                                                                |

|           | 2         | P2.0                     | Port 2 bit 0 input pin available when RPD (CONFIG0.2) is programmed as 0.                                                                                                                                                                                                                                                                  |

| 2         |           | nRESET                   | nRESET pin is a Schmitt trigger input pin for hardware device reset. A low on this pin resets the device. nRESETpin has an internal pull-up resistor allowing power-on reset by simply connecting an external capacitor to GND.<br><b>Note:</b> It is recommended to use 10 k $\Omega$ pull-up resistor and 10 uF capacitor on nRESET pin. |

|           |           | UART0_RXD                | Serial port 0 receive input.                                                                                                                                                                                                                                                                                                               |

|           |           | P3.0                     | Port 3 bit 0 available when the internal oscillator is used as the system clock.                                                                                                                                                                                                                                                           |

| 3         | -         | ADC_CH1                  | ADC input channel 1.                                                                                                                                                                                                                                                                                                                       |

|           |           | INT0                     | External interrupt 0 input.                                                                                                                                                                                                                                                                                                                |

|           |           | OSCIN                    | If the ECLK mode is enabled, Xin is the external clock input pin.                                                                                                                                                                                                                                                                          |

## Note:

nuvoton

- 1. All I/O pins can be configured as a interrupt pin. This feature is not listed in multi-function description.

- 2. UARTO\_TXD and UARTO\_RXD pins are software exchangeable by UARTOPX (AUXR1.2).

- 3. [I2C] alternate function remapping option. I2C pins is software switched by I2CPX (I2CON.0).

- 4. [STADC] alternate function remapping option. STADC pin is software switched by STADCPX(ADCCON1.6).

- 5. PIOx register decides which pins are PWM or GPIO.

- 6. UART1\_TXD and UART1\_RXD pins are software exchangeable by UART1PX (AUXR1.1).

Table 4.2-1 Pin Description

## 5 BLOCK DIAGRAM

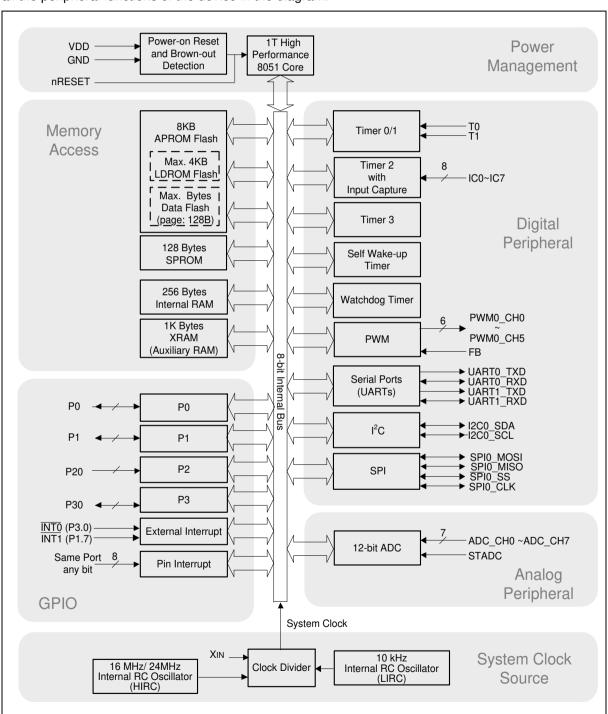

## 5.1 MS51BA9AE / MS51DA9AE BLOCK DIAGRAM

Figure 5.1-1 shows the MS51 functional block diagram and gives the outline of the device. User can find all the peripheral functions of the device in the diagram.

Figure 5.1-1 Functional Block Diagram

## **FUNCTION DESCRIPTION**

#### 6.1 **Memory Organization**

nuvoTon

A standard 80C51 based microcontroller divides the memory into two different sections, Program Memory and Data Memory. The Program Memory is used to store the instruction codes, whereas the Data Memory is used to store data or variations during the program execution.

The Data Memory occupies a separate address space from Program Memory. In MS51, there are 256 Bytes of internal scratch-pad RAM. For many applications those need more internal RAM, the MS51 provides another on-chip 1K Bytes of RAM, which is called XRAM, accessed by MOVX instruction.

The whole embedded flash, functioning as Program Memory, is divided into three blocks: Application ROM (APROM) normally for User Code, Loader ROM (LDROM) normally for Boot Code, and CONFIG bytes for hardware initialization. Actually, APROM and LDROM function in the same way but have different size. Each block is accumulated page by page and the page size is 128 Bytes. The flash control unit supports Erase, Program, and Read modes. The external writer tools though specific I/O pins, In-Application-Programming (IAP), or In-System-Programming (ISP) can both perform these modes.

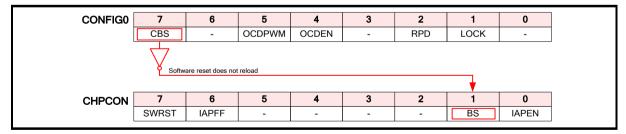

# 6.2 Config Bytes

The MS51 has several hardware configuration bytes, called CONFIG, those are used to configure the hardware options such as the security bits, system clock source, and so on. These hardware options can be re-configured through the parallel Writer, In-Circuit-Programming (ICP), or In-Application-Programming (IAP). Several functions, which are defined by certain CONFIG bits are also available to be re-configured by SFR. Therefore, there is a need to load such CONFIG bits into respective SFR bits. Such loading will occur after resets. These SFR bits can be continuously controlled via user's software.

nuvoTon

| 7   | 6 | 5      | 4     | 3 | 2   | 1    | 0 |

|-----|---|--------|-------|---|-----|------|---|

| CBS | - | OCDPWM | OCDEN | - | RPD | LOCK | - |

| R/W | - | R/W    | R/W   | - | R/W | R/W  | - |

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CBS    | CONFIG boot select This bit defines from which block that MCU re-boots after resets except software reset.  1 = MCU will re-boot from APROM after resets except software reset.  0 = MCU will re-boot from LDROM after resets except software reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | OCDPWM | PWM output state under OCD halt This bit decides the output state of PWM when OCD halts CPU.  1 = Tri-state pins those are used as PWM outputs.  0 = PWM continues.  Note that this bit is valid only when the corresponding PIO bit of PWM channel is set as 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | OCDEN  | OCD enable 1 = OCD Disabled. 0 = OCD Enabled. Note: If MCU run in OCD debug mode and OCDEN = 0, hard fault reset will be disabled and only Hard F flag be asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | RPD    | Reset pin disable 1 = The reset function of P2.0/Nrst pin Enabled. P2.0/Nrst functions as the external reset pin. 0 = The reset function of P2.0/Nrst pin Disabled. P2.0/Nrst functions as an input-only pin P2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1   | LOCK   | Chip lock enable  1 = Chip is unlocked. Flash Memory is not locked. Their contents can be read out through a parallel Writer/ICP programmer.  0 = Chip is locked. Whole Flash Memory is locked. Their contents read through a parallel Writer or ICP programmer will be all blank (FFH). Programming to Flash Memory is invalid. Note that CONFIG bytes are always unlocked and can be read. Hence, once the chip is locked, the CONFIG bytes cannot be erased or programmed individually. The only way to disable chip lock is execute "whole chip erase". However, all data within the Flash Memory and CONFIG bits will be erased when this procedure is executed.  If the chip is locked, it does not alter the IAP function. |

Figure 6.2-1 CONFIG0 Any Reset Reloading

| 7 | 6 | 5 | 4 | 3 | 2 | 1           | 0 |

|---|---|---|---|---|---|-------------|---|

| - | - | - | - | - |   | LDSIZE[2:0] |   |

| - | - | = | - | - |   | R/W         |   |

| Bit | Name        | Description                                                                                                                                                                                                                          |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0 | LDSIZE[2:0] | LDROM size select 111 = No LDROM. APROM is 8 Kbytes. 110 = LDROM is 1 Kbytes. APROM is 7 Kbytes. 101 = LDROM is 2 Kbytes. APROM is 6 Kbytes. 100 = LDROM is 3 Kbytes. APROM is 5 Kbytes. 0xx = LDROM is 4 Kbytes. APROM is 4 Kbytes. |

nuvoTon

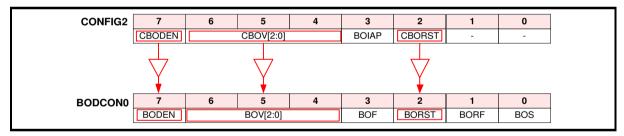

| 7      | 6 | 5         | 4 | 3     | 2      | 1 | 0 |

|--------|---|-----------|---|-------|--------|---|---|

| CBODEN | - | CBOV[2:0] |   | BOIAP | CBORST | - | - |

| R/W    | = | R/W       |   | R/W   | R/W    | - | - |

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CBODEN    | CONFIG brown-out detect enable  1 = Brown-out detection circuit on.  0 = Brown-out detection circuit off.                                                                                                                                                                                                                                                                   |

| 5:4 | CBOV[1:0] | CONFIG brown-out voltage select $11 = V_{BOD}$ is 2.2V. $10 = V_{BOD}$ is 2.7V. $01 = V_{BOD}$ is 3.7V. $00 = V_{BOD}$ is 4.4V.                                                                                                                                                                                                                                             |

| 3   | BOIAP     | Brown-out inhibiting IAP This bit decides whether IAP erasing or programming is inhibited by brown-out status. This bit is valid only when brown-out detection is enabled. $1 = \text{IAP erasing or programming is inhibited if V}_{\text{DD}} \text{ is lower than V}_{\text{BOD}}.$ $0 = \text{IAP erasing or programming is allowed under any workable V}_{\text{DD}}.$ |

| 2   | CBORST    | CONFIG brown-out reset enable This bit decides whether a brown-out reset is caused by a power drop below V <sub>BOD</sub> .  1 = Brown-out reset Enabled.  0 = Brown-out reset Disabled.                                                                                                                                                                                    |

Figure 6.2-2 CONFIG2 Power-On Reset Reloading

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|

| WDTEN[3:0] |   |   |   | - | - | - | - |

| R/W        |   |   | - | - | - | - |   |

| Bit | Name       | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | WDTEN[3:0] | WDT enable This field configures the WDT behavior after MCU execution.  1111 = WDT is Disabled. WDT can be used as a general purpose timer via software control.  0101 = WDT is Enabled as a time-out reset timer and it stops running during Idle or Powerdown mode.  Others = WDT is Enabled as a time-out reset timer and it keeps running during Idle or Powerdown mode. |

| 3:0 | -          | Reserved                                                                                                                                                                                                                                                                                                                                                                     |

#### 6.3 **System Manager**

#### 6.3.1 **Clock System**

nuvoton

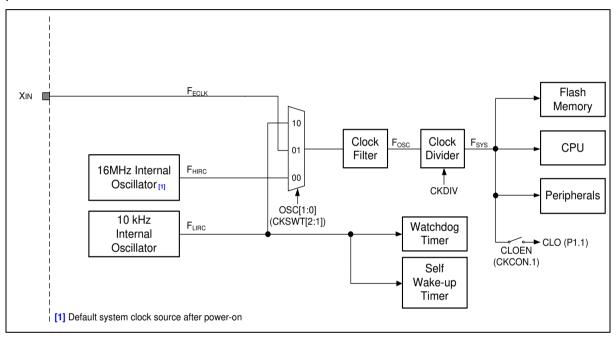

The MS51 has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. The MS51 provides three options of the system clock sources including internal oscillator, or external clock from XIN pin via software. The MS51 is embedded with two internal oscillators: one 10 kHz low-speed and one 16 MHz high-speed, which is factory trimmed to ±2% under all conditions. A clock divider CKDIV is also available on MS51 for adjustment of the flexibility between power consumption and operating performance.

Figure 6.3-1 Clock System Block Diagram

## 6.4 Flash Memory Control

## 6.4.1 In-Application-Programming (IAP)

Unlike RAM's real-time operation, to update flash data often takes long time. Furthermore, it is a quite complex timing procedure to erase, program, or read flash data. The MS51 carried out the flash operation with convenient mechanism to help user re-programming the flash content by In-Application-Programming (IAP). IAP is an in-circuit electrical erasure and programming method through software.

After IAP enabling by setting IAPEN (CHPCON.0 with TA protected) and setting the enable bit in IAPUEN that allows the target block to be updated, user can easily fill the 16-bit target address in IAPAH and IAPAL, data in IAPFD, and command in IAPCN. Then the IAP is ready to begin by setting a triggering bit IAPGO (IAPTRG.0). Note that IAPTRG is also TA protected. At this moment, the CPU holds the Program Counter and the built-in IAP automation takes over to control the internal charge-pump for high voltage and the detail signal timing. The erase and program time is internally controlled disregard of the operating voltage and frequency. Nominally, a page-erase time is 5 ms and a byte-program time is 23.5 µs. After IAP action completed, the Program Counter continues to run the following instructions. The IAPGO bit will be automatically cleared. An IAP failure flag, IAPFF (CHPCON.6), can be check whether the previous IAP operation was successful or not. Through this progress, user can easily erase, program, and verify the Flash Memory by just taking care of pure software.

## 6.4.2 In-Circuit-Programming (ICP)

The Flash Memory can be programmed by "In-Circuit-Programming" (ICP). If the product is just under development or the end product needs firmware updating in the hand of an end customer, the hardware programming mode will make repeated programming difficult and inconvenient. ICP method makes it easy and possible without removing the microcontroller from the system. ICP mode also allows customers to manufacture circuit boards with un-programmed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a customized firmware.

There are three signal pins, nRESET, ICE\_DAT, and ICE\_CLK, involved in ICP function. nRESET is used to enter or exit ICP mode. ICE\_DAT is the data input and output pin. ICE\_CLK is the clock input pin, which synchronizes the data shifted in to or out from MCU under programming. User should leave these three pins plus VDD and GND pins on the circuit board to make ICP possible.

Nuvoton provides ICP tool for MS51, which enables user to easily perform ICP through Nuvoton ICP programmer. The ICP programmer developed by Nuvoton has been optimized according to the electric characteristics of MCU. It also satisfies the stability and efficiency during production progress. For more details, please visit Nuvoton 8-bit Microcontroller website: <a href="Nuvoton 80C51 Microcontroller Technical Support">Nuvoton 80C51 Microcontroller Technical Support</a>.

## 6.4.3 On-Chip-Debugger (OCD)

The MS51 is embedded in an on-chip-debugger (OCD) providing developers with a low cost method for debugging user code, which is available on each package. The OCD gives debug capability of complete program flow control with eight hardware address breakpoints, single step, free running, and non-intrusive commands for memory access. The OCD system does not occupy any locations in the memory map and does not share any on-chip peripherals.

#### 6.5 **General Purpose I/O (GPIO)**

#### 6.5.1 **GPIO Mode**

nuvoTon

The MS51 has a maximum of 43 general purpose I/O pins which 40 bit-addressable general I/O pins grouped as 5 ports, P0 to P4, and 7 general I/O pins grouped as P5. Each port has its port control register (Px register). The writing and reading of a port control register have different meanings. A write to port control register sets the port output latch logic value, whereas a read gets the port pin logic state. These four modes are quasi-bidirectional (standard 8051 port structure), push-pull, input-only, and open-drain modes. Each port spends two special function registers PxM1 and PxM2 to select the I/O mode of port Px. The list below illustrates how to select the I/O mode of Px.n. Note that the default configuration of is input-only (high-impedance) after any reset.

| PnM1.X <sup>[1]</sup>                  | PnM2.X <sup>[1]</sup>               | I/O Type                    |  |  |  |

|----------------------------------------|-------------------------------------|-----------------------------|--|--|--|

| 0                                      | 0                                   | Quasi-bidirectional         |  |  |  |

| 0                                      | 1                                   | Push-pull                   |  |  |  |

| 1                                      | 0                                   | Input-only (high-impedance) |  |  |  |

| 1                                      | 1                                   | Open-drain                  |  |  |  |

| <b>NOTE1:</b> $N = 0 \sim 5$ , $x = 0$ | <b>NOTE1:</b> $N = 0.5$ , $x = 0.7$ |                             |  |  |  |

Table 6.5-1 Configuration for Different I/O Modes

All I/O pins can be selected as TTL level inputs or Schmitt triggered inputs by selecting corresponding bit in PxS register. Schmitt triggered input has better glitch suppression capability. All I/O pins also have bit-controllable, slew rate select ability via software. The control registers are PxSR. By default, the slew rate is slow. If user would like to increase the I/O output speed, setting the corresponding bit in PxSR, the slew rate is selected in a faster level.

## For example:

```

POM1 | = 0x40;

POM2 &= 0xBF;

//Set P0.6 as input only mode

```

## 6.6 Timer

## 6.6.1 Timer/Counter 0 And 1

Timer/Counter 0 and 1 on MS51 are two 16-bit Timers/Counters. Each of them has two 8-bit registers those form the 16-bit counting register. For Timer/Counter 0 they are TH0, the upper 8-bit register, and TL0, the lower 8-bit register. Similarly Timer/Counter 1 has two 8-bit registers, TH1 and TL1. TCON and TMOD can configure modes of Timer/Counter 0 and 1.

The Timer or Counter function is selected by the  $C/\overline{T}$  bit in TMOD. Each Timer/Counter has its own selection bit. TMOD.2 selects the function for Timer/Counter 0 and TMOD.6 selects the function for Timer/Counter 1

When configured as a "Timer", the timer counts the system clock cycles. The timer clock is 1/12 of the system clock (Fsys) for standard 8051 capability or direct the system clock for enhancement, which is selected by T0M (CKCON.3) bit for Timer 0 and T1M (CKCON.4) bit for Timer 1. In the "Counter" mode, the countering register increases on the falling edge of the external input pin T0. If the sampled value is high in one clock cycle and low in the next, a valid 1-to-0 transition is recognized on T0 or T1 pin.

The Timers 0 and 1 can be configured to automatically to toggle output whenever a timer overflow occurs. The same device pins that are used for the T0 and T1 count inputs are also used for the timer toggle outputs. This function is enabled by control bits T0OE and T1OE in the CKCON register, and apply to Timer 0 and Timer 1 respectively. The port outputs will be logic 1 prior to the first timer overflow when this mode is turned on. In order for this mode to function, the  $C/\overline{T}$  bit should be cleared selecting the system clock as the clock source for the timer.

Note that the TH0 (TH1) and TL0 (TL1) are accessed separately. It is strongly recommended that in mode 0 or 1, user should stop Timer temporally by clearing TR0 (TR1) bit before reading from or writing to TH0 (TH1) and TL0 (TL1). The free-running reading or writing may cause unpredictable result.

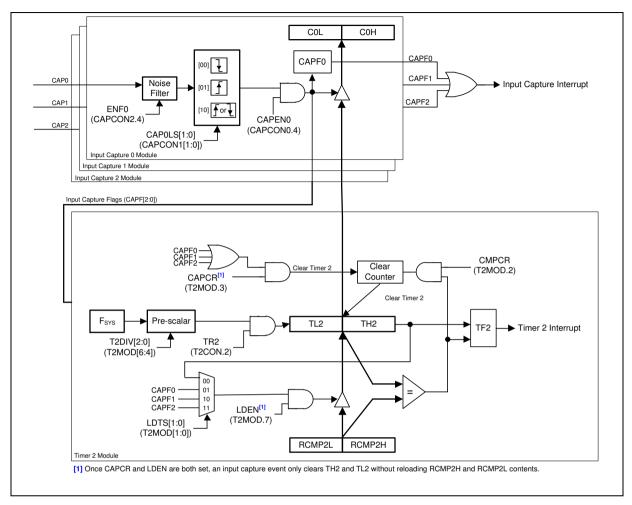

## 6.6.2 Timer2 and Input Capture

Timer 2 is a 16-bit up counter cascaded with TH2, the upper 8 bits register, and TL2, the lower 8 bit register. Equipped with RCMP2H and RCMP2L, Timer 2 can operate under compare mode and autoreload mode selected by CM/RL2 (T2CON.0). An 3-channel input capture module makes Timer 2 detect and measure the width or period of input pulses. The results of 3 input captures are stores in C0H and C0L, C1H and C1L, C2H and C2L individually. The clock source of Timer 2 is from the system clock pre-scaled by a clock divider with 8 different scales for wide field application. The clock is enabled when TR2 (T2CON.2) is 1, and disabled when TR2 is 0. The following registers are related to Timer 2 function.