EN: This Datasheet is presented by the manufacturer.

Please visit our website for pricing and availability at www.hestore.hu.

# INTEGRATED CIRCUITS

# DATA SHEET

# UDA1334ATS Low power audio DAC with PLL

Product specification Supersedes data of 2000 Feb 09 2000 Jul 31

# Low power audio DAC with PLL

# **UDA1334ATS**

| CONTE | NTS                             | 9    | LIMITING VALUES                              |

|-------|---------------------------------|------|----------------------------------------------|

| 1     | FEATURES                        | 10   | HANDLING                                     |

| 1.1   | General                         | 11   | THERMAL CHARACTERISTICS                      |

| 1.2   | Multiple format data interface  | 12   | QUALITY SPECIFICATION                        |

| 1.3   | DAC digital features            | 13   | DC CHARACTERISTICS                           |

| 1.4   | Advanced audio configuration    | 14   | AC CHARACTERISTICS                           |

| 1.5   | PLL system clock generation     | 14.1 | Analog                                       |

| 2     | APPLICATIONS                    | 14.2 | Timing                                       |

| 3     | GENERAL DESCRIPTION             | 15   | APPLICATION INFORMATION                      |

| 4     | ORDERING INFORMATION            | 16   | PACKAGE OUTLINE                              |

| 5     | QUICK REFERENCE DATA            | 17   | SOLDERING                                    |

| 6     | BLOCK DIAGRAM                   | 17.1 | Introduction to soldering surface mount      |

| 7     | PINNING                         | 17.1 | packages                                     |

| 8     | FUNCTIONAL DESCRIPTION          | 17.2 | Reflow soldering                             |

| 8.1   | System clock                    | 17.3 | Wave soldering                               |

| 8.1.1 | Audio mode                      | 17.4 | Manual soldering                             |

| 8.1.2 | Video mode                      | 17.5 | Suitability of surface mount IC packages for |

| 8.2   | Interpolation filter            |      | wave and reflow soldering methods            |

| 8.3   | Noise shaper                    | 18   | DATA SHEET STATUS                            |

| 8.4   | Filter stream DAC               | 19   | DISCLAIMERS                                  |

| 8.5   | Power-on reset                  |      |                                              |

| 8.6   | Feature settings                |      |                                              |

| 8.6.1 | Digital interface format select |      |                                              |

| 8.6.2 | De-emphasis control             |      |                                              |

| 8.6.3 | Mute control                    |      |                                              |

# Low power audio DAC with PLL

UDA1334ATS

#### **FEATURES**

#### 1.1 General

- 2.4 to 3.6 V power supply voltage

- On-board PLL to generate the internal system clock:

- Operates as an asynchronous DAC, regenerating the internal clock from the WS signal (called audio mode)

- Generates audio related system clock (output) based on 32, 48 or 96 kHz sampling frequency (called video mode).

- · Integrated digital filter plus DAC

- Supports sample frequencies from 16 to 100 kHz in asynchronous DAC mode

- · No analog post filtering required for DAC

- · Easy application

- · SSOP16 package.

#### 1.2 Multiple format data interface

- I<sup>2</sup>S-bus and LSB-justified format compatible

- 1f<sub>s</sub> input data rate.

#### DAC digital features

- Digital de-emphasis for 44.1 kHz sampling frequency

- · Mute function.

#### Advanced audio configuration

• High linearity, wide dynamic range and low distortion.

#### 1.5 PLL system clock generation

- Integrated low jitter PLL for use in applications in which there is digital audio data present but the system cannot provide an audio related system clock. This mode is called audio mode.

- The PLL can generate  $256 \times 48 \text{ kHz}$  and  $384 \times 48 \text{ kHz}$ from a 27 MHz input clock. This mode is called video mode.

BITSTREAM CONVERSION

#### **APPLICATIONS**

This audio DAC is excellently suitable for digital audio portable application, specially in applications in which an audio related system clock is not present.

#### **GENERAL DESCRIPTION**

The UDA1334ATS is a single chip 2 channel digital-to-analog converter employing bitstream conversion techniques, including an on-board PLL. The extremely low power consumption and low voltage requirements make the device eminently suitable for use in low-voltage low-power portable digital audio equipment which incorporates a playback function.

The UDA1334ATS supports the I<sup>2</sup>S-bus data format with word lengths of up to 24 bits and the LSB-justified serial data format with word lengths of 16, 20 and 24 bits.

The UDA1334ATS has basic features such as de-emphasis (44.1 kHz sampling frequency, only supported in audio mode) and mute.

#### ORDERING INFORMATION

| TYPE       |                                                                            | PACKAGE     |         |  |

|------------|----------------------------------------------------------------------------|-------------|---------|--|

| NUMBER     | NAME                                                                       | DESCRIPTION | VERSION |  |

| UDA1334ATS | SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm S |             |         |  |

2000 Jul 31 3

# Low power audio DAC with PLL

UDA1334ATS

#### **5 QUICK REFERENCE DATA**

| SYMBOL               | PARAMETER                                                  | CONDITIONS                                          | MIN. | TYP. | MAX. | UNIT |

|----------------------|------------------------------------------------------------|-----------------------------------------------------|------|------|------|------|

| Supplies             |                                                            |                                                     | •    | •    | •    | •    |

| $V_{DDA}$            | DAC analog supply voltage                                  |                                                     | 2.4  | 3.0  | 3.6  | ٧    |

| $V_{DDD}$            | digital supply voltage                                     |                                                     | 2.4  | 3.0  | 3.6  | ٧    |

| I <sub>DDA</sub>     | DAC analog supply current                                  | audio mode                                          | _    | 3.5  | _    | mA   |

|                      |                                                            | video mode                                          | _    | 3.5  | _    | mA   |

| I <sub>DDD</sub>     | digital supply current                                     | audio mode                                          | _    | 2.5  | _    | mA   |

|                      |                                                            | video mode                                          | -    | 4.5  | -    | mA   |

| T <sub>amb</sub>     | ambient temperature                                        |                                                     | -40  | _    | +85  | °C   |

| Digital-to-anal      | og converter (V <sub>DDA</sub> = V <sub>DDD</sub> = 3.0 V) | •                                                   | •    | •    | •    | •    |

| V <sub>o(rms)</sub>  | output voltage (RMS value)                                 | at 0 dB (FS) digital input; note 1                  | _    | 900  | _    | mV   |

| (THD+N)/S            | total harmonic distortion-plus-noise to                    | f <sub>s</sub> = 44.1 kHz; at 0 dB                  | _    | -90  | _    | dB   |

| signal ratio         | signal ratio                                               | f <sub>s</sub> = 44.1 kHz; at -60 dB;<br>A-weighted | _    | -40  | -    | dB   |

|                      |                                                            | f <sub>s</sub> = 96 kHz; at 0 dB                    | _    | -85  | _    | dB   |

|                      |                                                            | f <sub>s</sub> = 96 kHz; at -60 dB;<br>A-weighted   | _    | -38  | -    | dB   |

| S/N                  | signal-to-noise ratio                                      | f <sub>s</sub> = 44.1 kHz; code = 0;<br>A-weighted  | _    | 100  | -    | dB   |

|                      |                                                            | f <sub>s</sub> = 96 kHz; code = 0;<br>A-weighted    | _    | 98   | -    | dB   |

| $\alpha_{\text{CS}}$ | channel separation                                         |                                                     | _    | 100  | -    | dB   |

| Power dissipa        | ition (at f <sub>s</sub> = 44.1 kHz)                       |                                                     |      |      |      |      |

| P                    | power dissipation                                          | audio mode                                          | _    | 18   | _    | mW   |

|                      |                                                            | video mode                                          | _    | 24   | _    | mW   |

#### Note

1. The output voltage of the DAC scales proportionally to the power supply voltage.

2000 Jul 31

# Low power audio DAC with PLL

# UDA1334ATS

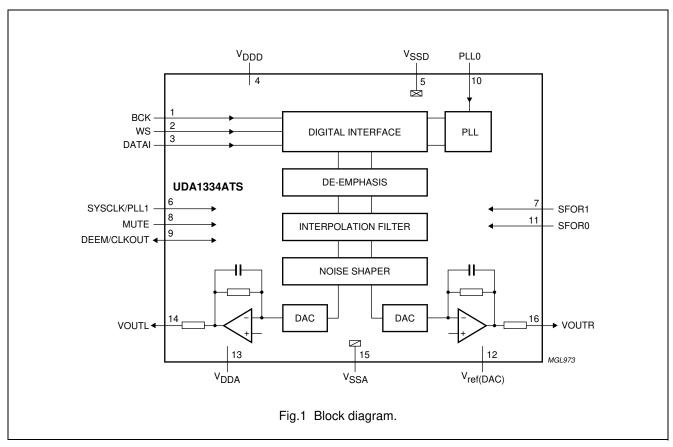

#### 6 BLOCK DIAGRAM

# Low power audio DAC with PLL

# UDA1334ATS

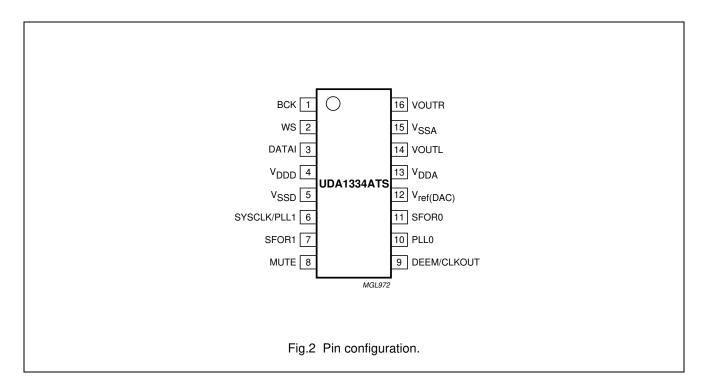

#### 7 PINNING

| SYMBOL                | PIN | PAD TYPE                              | DESCRIPTION                                                             |  |

|-----------------------|-----|---------------------------------------|-------------------------------------------------------------------------|--|

| BCK                   | 1   | 5 V tolerant digital input pad        | bit clock input                                                         |  |

| WS                    | 2   | 5 V tolerant digital input pad        | word select input                                                       |  |

| DATAI                 | 3   | 5 V tolerant digital input pad        | serial data input                                                       |  |

| $V_{DDD}$             | 4   | digital supply pad                    | digital supply voltage                                                  |  |

| V <sub>SSD</sub>      | 5   | digital ground pad                    | digital ground                                                          |  |

| SYSCLK/PLL1           | 6   | 5 V tolerant digital input pad        | system clock input in video mode/PLL mode control 1 input in audio mode |  |

| SFOR1                 | 7   | 5 V tolerant digital input pad        | serial format select 1 input                                            |  |

| MUTE                  | 8   | 5 V tolerant digital input pad        | mute control input                                                      |  |

| DEEM/CLKOUT           | 9   | 5 V tolerant digital input/output pad | de-emphasis control input in audio mode/clock output in video mode      |  |

| PLL0                  | 10  | 3-level input pad; note 1             | PLL mode control 0 input                                                |  |

| SFOR0                 | 11  | digital input pad; note 1             | serial format select 0 input                                            |  |

| V <sub>ref(DAC)</sub> | 12  | analog pad                            | DAC reference voltage                                                   |  |

| $V_{DDA}$             | 13  | analog supply pad                     | DAC analog supply voltage                                               |  |

| VOUTL                 | 14  | analog output pad                     | DAC output left                                                         |  |

| V <sub>SSA</sub>      | 15  | analog ground pad                     | DAC analog ground                                                       |  |

| VOUTR                 | 16  | analog output pad                     | DAC output right                                                        |  |

#### Note

1. Because of test issues these pads are not 5 V tolerant and both pads should be at power supply voltage level or at a maximum of 0.5 V above that level.

# Low power audio DAC with PLL

#### UDA1334ATS

#### 8 FUNCTIONAL DESCRIPTION

#### 8.1 System clock

The UDA1334ATS incorporates a PLL capable of generating the system clock. The UDA1334ATS can operate in 2 modes:

- It operates as an asynchronous DAC, which means the device regenerates the internal clocks using a PLL from the incoming WS signal. This mode is called audio mode.

- It generates the internal clocks from a 27 MHz clock input, based on 32, 48 and 96 kHz sampling frequencies. This mode is called video mode.

In video mode, the digital audio input is slave, which means that the system must generate the BCK and WS signals from the output clock available at pin CLKOUT of the UDA1334ATS. The digital audio signals should be frequency locked to the CLKOUT signal.

#### Remarks:

- The WS edge MUST fall on the negative edge of the BCK at all times for proper operation of the digital I/O data interface

- 2. For LSB-justified formats it is important to have a WS signal with a duty factor of 50%.

#### 8.1.1 AUDIO MODE

Audio mode is enabled by setting pin PLL0 to LOW. De-emphasis can be activated via pin DEEM/CLKOUT according to Table 5.

In audio mode, pin SYSCLK/PLL1 is used to set the sampling frequency range as given in Table 1.

**Table 1** Sampling frequency range in audio mode

| SYSCLK/PLL1 | SELECTION                             |

|-------------|---------------------------------------|

| LOW         | $f_S = 16 \text{ to } 50 \text{ kHz}$ |

| HIGH        | f <sub>s</sub> = 50 to 100 kHz        |

#### 8.1.2 VIDEO MODE

In video mode, the master clock is a 27 MHz external clock (as is available in video environment). A clock-out signal is generated at pin DEEM/CLKOUT. The output frequency can be selected using pin PLL0. The output frequency is either 12.228 MHz (256  $\times$  48 kHz) with pin PLL0 being at MID level or 18.432 MHz (384  $\times$  48 kHz) with pin PLL0 being HIGH, as given in Table 2.

Table 2 Clock output selection in video mode

| PLL0 | SELECTION                |

|------|--------------------------|

| MID  | 12.228 MHz clock; note 1 |

| HIGH | 18.432 MHz clock; note 2 |

| LOW  | audio mode               |

#### **Notes**

- 1. The supported sampling frequencies are: 96, 48 and 24 kHz or 64, 32 and 16 kHz.

- The supported sampling frequencies are: 96, 48 and 24 kHz; 72 and 36 kHz or 32 kHz.

#### 8.2 Interpolation filter

The interpolation digital filter interpolates from  $1f_s$  to  $64f_s$  by cascading FIR filters (see Table 3).

Table 3

Interpolation filter characteristics

| ITEM             | CONDITION           | VALUE (dB) |  |

|------------------|---------------------|------------|--|

| Pass-band ripple | $0f_s$ to $0.45f_s$ | ±0.02      |  |

| Stop band        | >0.55f <sub>s</sub> | -50        |  |

| Dynamic range    | $0f_s$ to $0.45f_s$ | >114       |  |

#### 8.3 Noise shaper

The 5th-order noise shaper operates at  $64f_s$ . It shifts in-band quantization noise to frequencies well above the audio band. This noise shaping technique enables high signal-to-noise ratios to be achieved. The noise shaper output is converted into an analog signal using a Filter Stream DAC (FSDAC).

# Low power audio DAC with PLL

#### UDA1334ATS

#### 8.4 Filter stream DAC

The FSDAC is a semi-digital reconstruction filter that converts the 1-bit data stream of the noise shaper to an analog output voltage. The filter coefficients are implemented as current sources and are summed at virtual ground of the output operational amplifier. In this way very high signal-to-noise performance and low clock jitter sensitivity is achieved. No post filter is needed due to the inherent filter function of the DAC. On-board amplifiers convert the FSDAC output current to an output voltage signal capable of driving a line output.

The output voltage of the FSDAC scales proportionally to the power supply voltage.

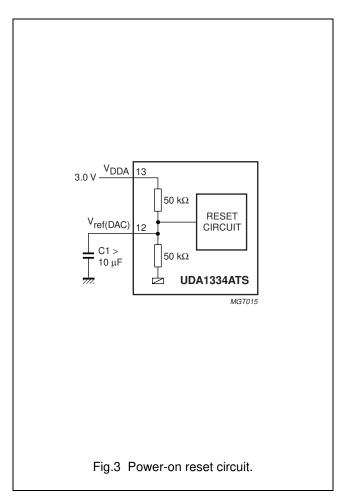

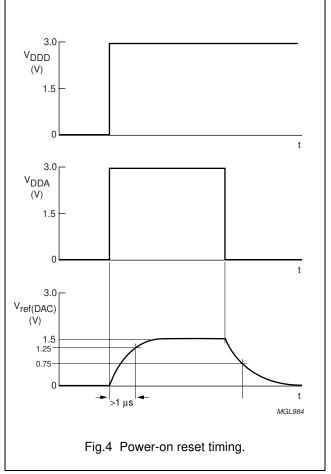

#### 8.5 Power-on reset

The UDA1334ATS has an internal Power-on reset circuit (see Fig.3) which resets the test control block.

The reset time (see Fig.4) is determined by an external capacitor which is connected between pin  $V_{ref(DAC)}$  and ground. The reset time should be at least 1  $\mu s$  for  $V_{ref(DAC)} <$  1.25 V. When  $V_{DDA}$  is switched off, the device will be reset again for  $V_{ref(DAC)} <$  0.75 V.

During the reset time the system clock should be running.

# Low power audio DAC with PLL

#### UDA1334ATS

#### 8.6 Feature settings

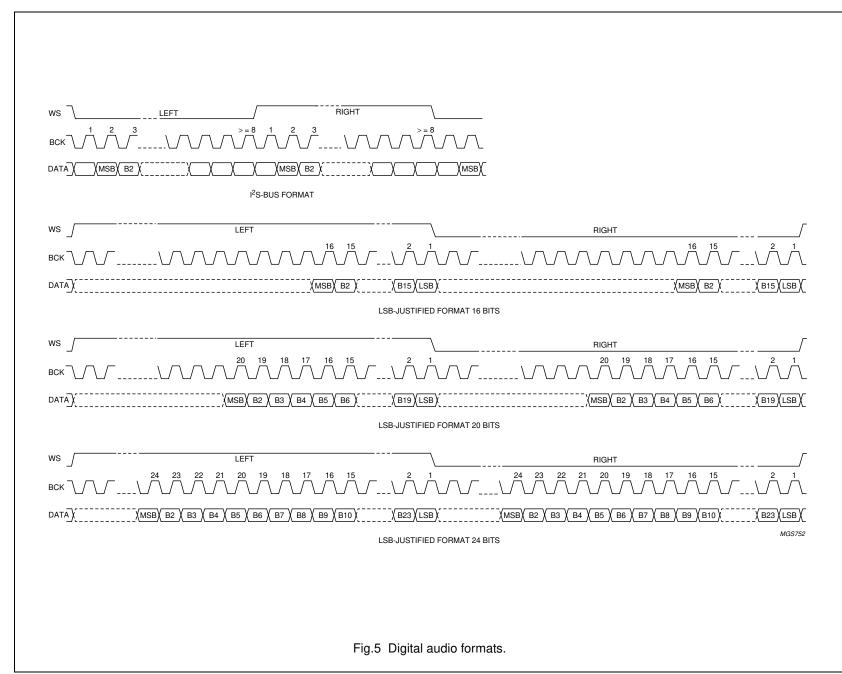

#### 8.6.1 DIGITAL INTERFACE FORMAT SELECT

The digital audio interface formats (see Fig.5) can be selected via pins SFOR1 and SFOR0 as shown in Table 4.

For the digital audio interface holds that the BCK frequency can be maximum 64 times WS frequency.

The WS signal must change at the negative edge of the BCK signal for all digital audio formats.

Table 4 Data format selection

| SFOR1 | SFOR0 | INPUT FORMAT                |

|-------|-------|-----------------------------|

| LOW   | LOW   | I <sup>2</sup> S-bus input  |

| LOW   | HIGH  | LSB-justified 16 bits input |

| HIGH  | LOW   | LSB-justified 20 bits input |

| HIGH  | HIGH  | LSB-justified 24 bits input |

#### 8.6.2 DE-EMPHASIS CONTROL

This function is only available in audio mode. In that case, pin DEEM/CLKOUT can be used to activate the digital de-emphasis for 44.1 kHz as given in Table 5.

Table 5

De-emphasis control (audio mode)

| DEEM/CLKOUT | FUNCTION        |

|-------------|-----------------|

| LOW         | de-emphasis off |

| HIGH        | de-emphasis on  |

#### 8.6.3 MUTE CONTROL

The output signal can be soft muted by setting pin MUTE to HIGH as given in Table 6.

Table 6 Mute control

| MUTE | FUNCTION |

|------|----------|

| LOW  | mute off |

| HIGH | mute on  |

# Low power audio DAC with PLL

NXP Semiconductors

# UDA1334ATS

# Low power audio DAC with PLL

UDA1334ATS

#### 9 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL                 | PARAMETER                      | CONDITIONS                                 | MIN.  | MAX.  | UNIT |

|------------------------|--------------------------------|--------------------------------------------|-------|-------|------|

| $V_{DD}$               | supply voltage                 | note 1                                     | _     | 4.0   | V    |

| T <sub>xtal(max)</sub> | maximum crystal temperature    |                                            | -     | 150   | °C   |

| T <sub>stg</sub>       | storage temperature            |                                            | -65   | +125  | °C   |

| T <sub>amb</sub>       | ambient temperature            |                                            | -40   | +85   | °C   |

| V <sub>es</sub>        | electrostatic handling voltage | human body model; note 2                   | -2000 | +2000 | V    |

|                        |                                | machine model; note 2                      | -250  | +250  | V    |

| I <sub>sc(DAC)</sub>   | short-circuit current of DAC   | note 3                                     |       |       |      |

|                        |                                | output short-circuited to V <sub>SSA</sub> | _     | 450   | mA   |

|                        |                                | output short-circuited to V <sub>DDA</sub> | _     | 300   | mA   |

#### **Notes**

- 1. All supply connections must be made to the same power supply.

- 2. ESD behaviour is tested according to JEDEC II standard.

- 3. Short-circuit test at  $T_{amb} = 0$  °C and  $V_{DDA} = 3$  V. DAC operation after short-circuiting cannot be warranted.

#### 10 HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

#### 11 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 145   | K/W  |

#### 12 QUALITY SPECIFICATION

In accordance with "SNW-FQ-611-E".

#### 13 DC CHARACTERISTICS

$V_{DDD} = V_{DDA} = 3.0 \text{ V}$ ;  $T_{amb} = 25 \,^{\circ}\text{C}$ ;  $R_L = 5 \, \text{k}\Omega$ ; all voltages with respect to ground (pins  $V_{SSA}$  and  $V_{SSD}$ ); unless otherwise specified.

| SYMBOL           | PARAMETER                 | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|------------------|---------------------------|------------|------|------|------|------|

| Supplies         |                           |            | •    |      | •    |      |

| $V_{DDA}$        | DAC analog supply voltage | note 1     | 2.4  | 3.0  | 3.6  | V    |

| $V_{DDD}$        | digital supply voltage    | note 1     | 2.4  | 3.0  | 3.6  | V    |

| I <sub>DDA</sub> | DAC analog supply current | audio mode | _    | 3.5  | _    | mA   |

|                  |                           | video mode | _    | 3.5  | _    | mA   |

| I <sub>DDD</sub> | digital supply current    | audio mode | _    | 2.5  | _    | mA   |

|                  |                           | video mode | _    | 4.5  | _    | mA   |

# Low power audio DAC with PLL

UDA1334ATS

| SYMBOL                | PARAMETER                                      | CONDITIONS                                       | MIN.                 | TYP.               | MAX.                | UNIT |

|-----------------------|------------------------------------------------|--------------------------------------------------|----------------------|--------------------|---------------------|------|

| Digital input pi      | ns: TTL compatible                             |                                                  | •                    |                    | •                   |      |

| V <sub>IH</sub>       | HIGH-level input voltage                       |                                                  | 2.0                  | _                  | 5.0                 | V    |

| $V_{IL}$              | LOW-level input voltage                        |                                                  | -0.5                 | _                  | +0.8                | V    |

| 16                    | input leakage current                          |                                                  | _                    | _                  | 1                   | μΑ   |

| C <sub>i</sub>        | input capacitance                              |                                                  | _                    | _                  | 10                  | pF   |

| 3-level input: p      | oin PLL0                                       |                                                  |                      |                    |                     |      |

| V <sub>IH</sub>       | HIGH-level input voltage                       |                                                  | $0.9V_{DDD}$         | _                  | $V_{DDD} + 0.5$     | V    |

| V <sub>IM</sub>       | MID-level input voltage                        |                                                  | $0.4V_{DDD}$         | _                  | 0.6V <sub>DDD</sub> | V    |

| V <sub>IL</sub>       | LOW-level input voltage                        |                                                  | -0.5                 | _                  | +0.5                | V    |

| Digital output        | pins                                           |                                                  |                      |                    |                     |      |

| V <sub>OH</sub>       | HIGH-level output voltage                      | $I_{OH} = -2 \text{ mA}$                         | 0.85V <sub>DDD</sub> | _                  | _                   | V    |

| V <sub>OL</sub>       | LOW-level output voltage                       | I <sub>OL</sub> = 2 mA                           | _                    | _                  | 0.4                 | V    |

| DAC                   |                                                |                                                  |                      |                    |                     |      |

| V <sub>ref(DAC)</sub> | reference voltage                              | with respect to V <sub>SSA</sub>                 | 0.45V <sub>DD</sub>  | 0.5V <sub>DD</sub> | 0.55V <sub>DD</sub> | V    |

| R <sub>o(ref)</sub>   | output resistance on pin V <sub>ref(DAC)</sub> |                                                  | _                    | 25                 | _                   | kΩ   |

| I <sub>o(max)</sub>   | maximum output current                         | $(THD + N)/S < 0.1\%;$ $R_L = 5 \text{ k}\Omega$ | _                    | 1.6                | -                   | mA   |

| R <sub>L</sub>        | load resistance                                |                                                  | 3                    | _                  | =                   | kΩ   |

| C <sub>L</sub>        | load capacitance                               | note 2                                           | _                    | _                  | 50                  | pF   |

#### **Notes**

- 1. All supply connections must be made to the same external power supply unit.

- 2. When the DAC drives a capacitive load above 50 pF, a series resistance of 100  $\Omega$  must be used to prevent oscillations in the output operational amplifier.

#### 14 AC CHARACTERISTICS

#### 14.1 Analog

$V_{DDD} = V_{DDA} = 3.0 \text{ V}$ ;  $f_i = 1 \text{ kHz}$ ;  $T_{amb} = 25 \text{ °C}$ ;  $R_L = 5 \text{ k}\Omega$ ; all voltages with respect to ground (pins  $V_{SSA}$  and  $V_{SSD}$ ); unless otherwise specified.

| SYMBOL              | PARAMETER                             | TYP.                                             | UNIT |    |

|---------------------|---------------------------------------|--------------------------------------------------|------|----|

| DAC                 |                                       |                                                  |      |    |

| V <sub>o(rms)</sub> | output voltage (RMS value)            | at 0 dB (FS) digital input; note 1               | 900  | mV |

| $\Delta V_{o}$      | unbalance between channels            |                                                  | 0.1  | dB |

| (THD + N)/S         | total harmonic                        | $f_s = 44.1 \text{ kHz}$ ; at 0 dB               | -90  | dB |

|                     | distortion-plus-noise to signal ratio | f <sub>s</sub> = 44.1 kHz; at -60 dB; A-weighted | -40  | dB |

|                     |                                       | $f_s = 96 \text{ kHz}$ ; at 0 dB                 | -85  | dB |

|                     |                                       | f <sub>s</sub> = 96 kHz; at -60 dB; A-weighted   | -38  | dB |

# Low power audio DAC with PLL

UDA1334ATS

| SYMBOL               | PARAMETER                    | CONDITIONS                                                     | TYP. | UNIT |

|----------------------|------------------------------|----------------------------------------------------------------|------|------|

| S/N                  | signal-to-noise ratio        | f <sub>s</sub> = 44.1 kHz; code = 0; A-weighted                | 100  | dB   |

|                      |                              | f <sub>s</sub> = 96 kHz; code = 0; A-weighted                  | 98   | dB   |

| $\alpha_{\text{CS}}$ | channel separation           |                                                                | 100  | dB   |

| PSRR                 | power supply rejection ratio | f <sub>ripple</sub> = 1 kHz; V <sub>ripple</sub> = 30 mV (p-p) | 60   | dB   |

#### Note

1. The output voltage of the DAC scales proportionally to the analog power supply voltage.

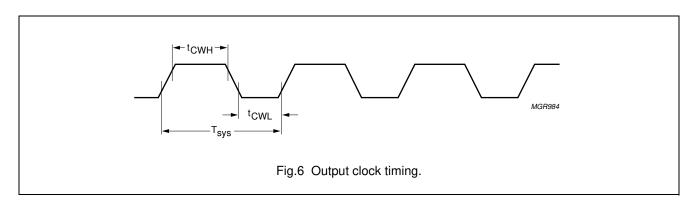

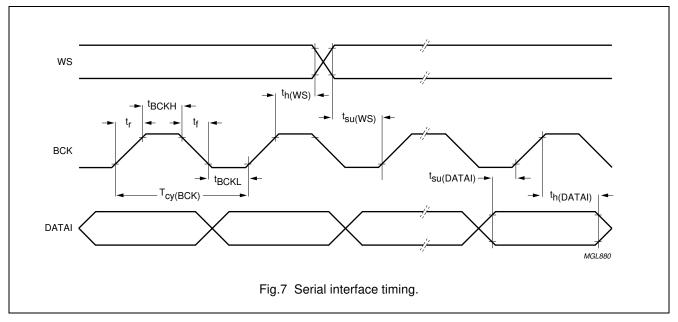

#### 14.2 Timing

$V_{DDD} = V_{DDA} = 2.4$  to 3.6 V;  $T_{amb} = -20$  to +85 °C;  $R_L = 5$  k $\Omega$ ; all voltages with respect to ground (pins  $V_{SSA}$  and  $V_{SSD}$ ); unless otherwise specified; note 1.

| SYMBOL                 | PARAMETER                   | CONDITIONS                  | MIN.                | TYP.  | MAX.                | UNIT |

|------------------------|-----------------------------|-----------------------------|---------------------|-------|---------------------|------|

| Output clock t         | iming in video mode (see Fi | g.6)                        | <u>.</u>            |       |                     |      |

| T <sub>sys</sub>       | output clock cycle          | f <sub>o</sub> = 12.228 MHz | _                   | 81.38 | _                   | ns   |

|                        |                             | f <sub>o</sub> = 18.432 MHz | _                   | 54.25 | _                   | ns   |

| t <sub>CWL</sub>       | output clock LOW time       | f <sub>o</sub> = 12.228 MHz | 0.3T <sub>sys</sub> | _     | 0.7T <sub>sys</sub> | ns   |

|                        |                             | f <sub>o</sub> = 18.432 MHz | 0.4T <sub>sys</sub> | _     | 0.6T <sub>sys</sub> | ns   |

| t <sub>CWH</sub>       | output clock HIGH time      | f <sub>o</sub> = 12.228 MHz | 0.3T <sub>sys</sub> | _     | 0.7T <sub>sys</sub> | ns   |

|                        |                             | f <sub>o</sub> = 18.432 MHz | 0.4T <sub>sys</sub> | _     | 0.6T <sub>sys</sub> | ns   |

| Serial input da        | ta timing (see Fig.7)       |                             |                     |       |                     |      |

| f <sub>BCK</sub>       | bit clock frequency         |                             | _                   | _     | 64f <sub>s</sub>    | Hz   |

| t <sub>BCKH</sub>      | bit clock HIGH time         |                             | 50                  | _     | _                   | ns   |

| t <sub>BCKL</sub>      | bit clock LOW time          |                             | 50                  | _     | _                   | ns   |

| t <sub>r</sub>         | rise time                   |                             | _                   | _     | 20                  | ns   |

| t <sub>f</sub>         | fall time                   |                             | _                   | _     | 20                  | ns   |

| t <sub>su(DATAI)</sub> | set-up time data input      |                             | 20                  | _     | _                   | ns   |

| t <sub>h(DATAI)</sub>  | hold time data input        |                             | 0                   | _     | _                   | ns   |

| t <sub>su(WS)</sub>    | set-up time word select     |                             | 20                  | _     | _                   | ns   |

| t <sub>h(WS)</sub>     | hold time word select       |                             | 10                  | _     | _                   | ns   |

#### Note

1. The typical value of the timing is specified for a sampling frequency of 44.1 kHz.

# Low power audio DAC with PLL

# UDA1334ATS

# Low power audio DAC with PLL

# UDA1334ATS

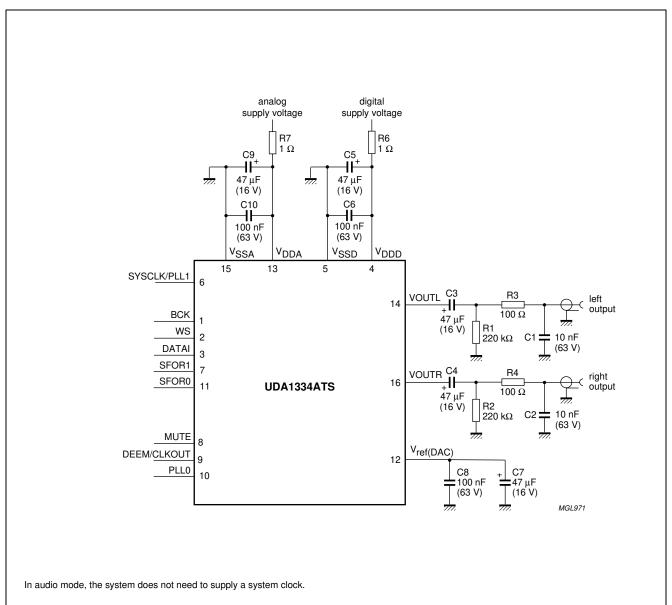

#### 15 APPLICATION INFORMATION

Fig.8 Audio mode application diagram.

# Low power audio DAC with PLL

# UDA1334ATS

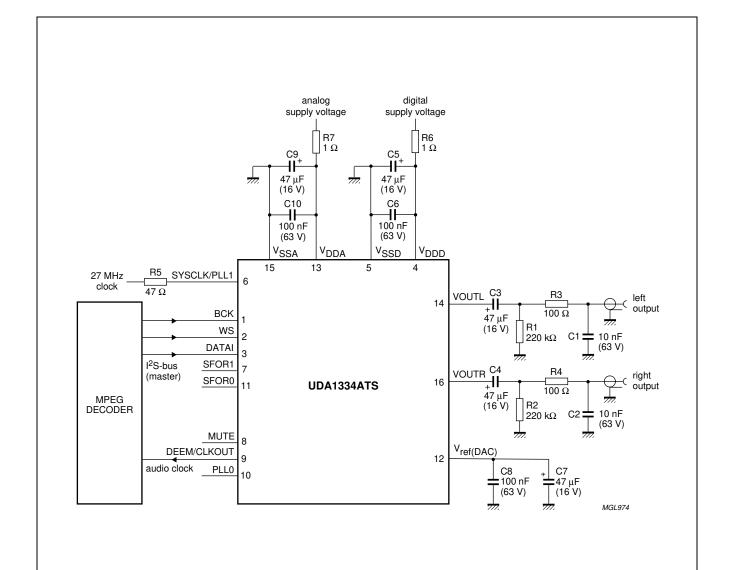

In video mode, a clock output signal is generated by the UDA1334ATS which is master for the audio signals in the system; the digital audio interface is slave, which means the system must generate the BCK and WS signal from the UDA1334ATS output clock.

Fig.9 Video mode application diagram.

# Low power audio DAC with PLL

# UDA1334ATS

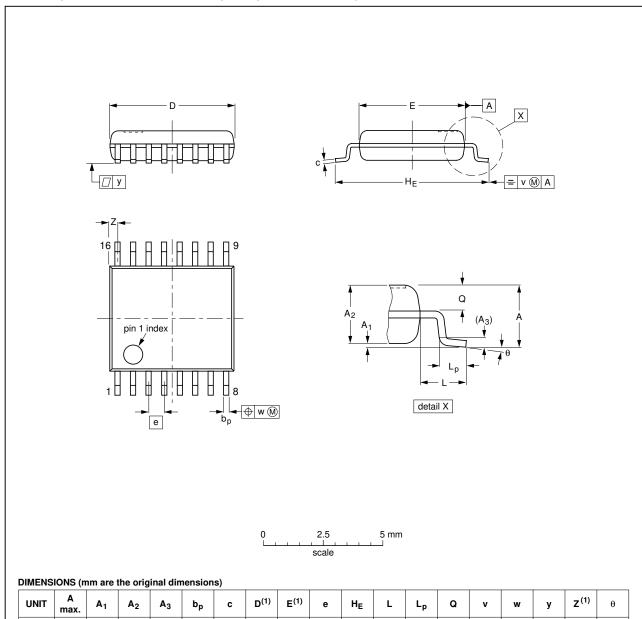

#### **16 PACKAGE OUTLINE**

SSOP16: plastic shrink small outline package; 16 leads; body width 4.4 mm

SOT369-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L | Lp           | Q            | v   | w    | у   | Z <sup>(1)</sup> | θ         |

|------|-----------|----------------|----------------|-----------------------|--------------|--------------|------------------|------------------|------|------------|---|--------------|--------------|-----|------|-----|------------------|-----------|

| mm   | 1.5       | 0.15<br>0.00   | 1.4<br>1.2     | 0.25                  | 0.32<br>0.20 | 0.25<br>0.13 | 5.3<br>5.1       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1 | 0.75<br>0.45 | 0.65<br>0.45 | 0.2 | 0.13 | 0.1 | 0.48<br>0.18     | 10°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.2 mm maximum per side are not included.

| OUTLINE  |     | REFER  | ENCES | EUROPEAN ISSUE DAT |                                 |  |  |

|----------|-----|--------|-------|--------------------|---------------------------------|--|--|

| VERSION  | IEC | JEDEC  | JEITA | PROJECTION         | ISSUE DATE                      |  |  |

| SOT369-1 |     | MO-152 |       |                    | <del>99-12-27</del><br>03-02-19 |  |  |

# Low power audio DAC with PLL

#### UDA1334ATS

#### 17 SOLDERING

# 17.1 Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards with high population densities. In these situations reflow soldering is often used.

#### 17.2 Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 230 °C.

#### 17.3 Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### 17.4 Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

# Low power audio DAC with PLL

UDA1334ATS

#### 17.5 Suitability of surface mount IC packages for wave and reflow soldering methods

| DACKACE                                      | SOLDERING METHOD                  |                       |  |  |  |

|----------------------------------------------|-----------------------------------|-----------------------|--|--|--|

| PACKAGE                                      | WAVE                              | REFLOW <sup>(1)</sup> |  |  |  |

| BGA, LFBGA, SQFP, TFBGA                      | not suitable                      | suitable              |  |  |  |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, SMS | not suitable <sup>(2)</sup>       | suitable              |  |  |  |

| PLCC <sup>(3)</sup> , SO, SOJ                | suitable                          | suitable              |  |  |  |

| LQFP, QFP, TQFP                              | not recommended <sup>(3)(4)</sup> | suitable              |  |  |  |

| SSOP, TSSOP, VSO                             | not recommended <sup>(5)</sup>    | suitable              |  |  |  |

#### **Notes**

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

# Low power audio DAC with PLL

UDA1334ATS

#### **18 DATA SHEET STATUS**

| DOCUMENT<br>STATUS(1)  | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITION                                                                            |

|------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| Objective data sheet   | Development                      | This document contains data from the objective specification for product development. |

| Preliminary data sheet | Qualification                    | This document contains data from the preliminary specification.                       |

| Product data sheet     | Production                       | This document contains the product specification.                                     |

#### Notes

- 1. Please consult the most recently issued document before initiating or completing a design.

- 2. The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 19 DISCLAIMERS

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe

property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

# Low power audio DAC with PLL

UDA1334ATS

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# **NXP Semiconductors**

provides High Performance Mixed Signal and Standard Product solutions that leverage its leading RF, Analog, Power Management, Interface, Security and Digital Processing expertise

#### **Customer notification**

This data sheet was changed to reflect the new company name NXP Semiconductors, including new legal definitions and disclaimers. No changes were made to the technical content, except for package outline drawings which were updated to the latest version.

#### **Contact information**

For additional information please visit: http://www.nxp.com

For sales offices addresses send e-mail to: salesaddresses@nxp.com

© NXP B.V. 2010

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands 753503/25/02/pp22 Date of release: 2000 Jul 31 Document order number: 9397 750 07238